Smarte Sensorik wird zukünftig dafür genutzt, die anfallenden Messwerte mit Hilfe von KI lokal zu Verarbeiten oder sich den Änderungen der Umwelt anzupassen. Im Projekt »Green ICT @ FMD« beschäftigen sich Wissenschaftlerinnen und Wissenschaftler des Fraunhofer IMS mit der energieeffizienten Implementierung von KI-Algorithmen. Der RISC-V Prozessor AIRISC (www.airisc.de) wurde deshalb über Befehlssatzerweiterungen und Coprozessoren für die extrem effiziente Berechnung von neuronalen Netzen erweitert. Für eine Applikation im Bereich der medizinischen Datenauswertung wurde dadurch ein Geschwindigkeitsvorteil von mehr als einem Faktor 7 bei lediglich etwa 10 % Overhead hinsichtlich des Flächen- und Energiebedarfes erzielt.

Ein Beitrag von:

Alexander Stanitzki

Leiter Geschäftsfeld Industry

Fraunhofer-Institut für Mikroelektronische Schaltungen und Systeme IMS

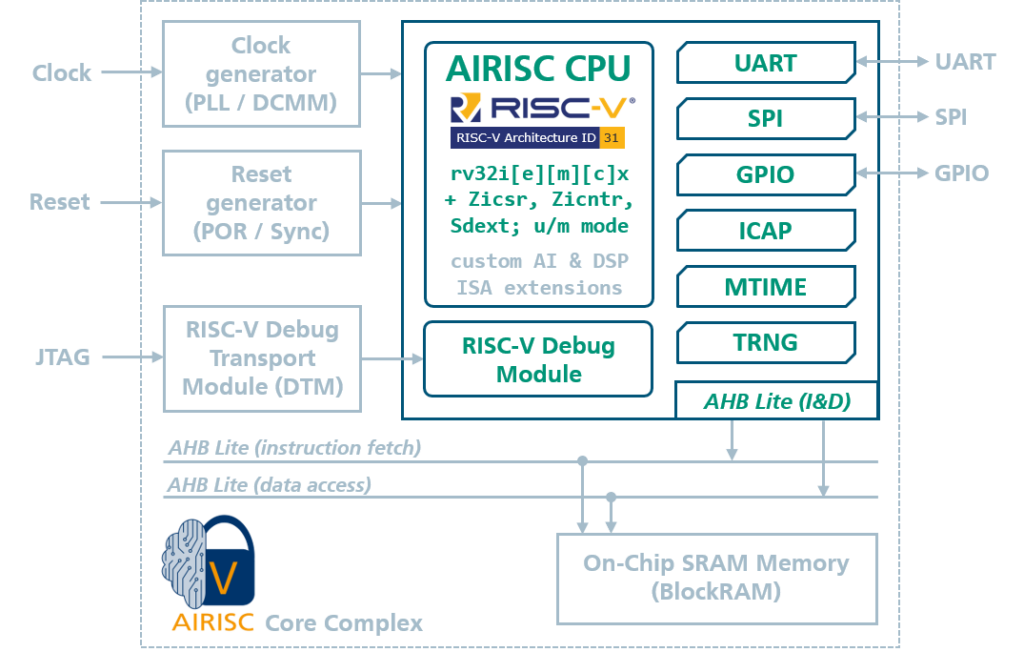

Bereits seit Anfang 2022 ist der RISC-V Prozessor AIRISC für Embedded- und Sensorikanwendungen des Fraunhofer IMS in der Basis-Variante als freier Core auf GitHub verfügbar und kann dort heruntergeladen werden[1]. Die freie Version steht unter der permissiven Solderpad-Lizenz und kommt mit fertigen Beispiel-Projekten für verschiedene FPGA-Entwicklungsboards. Die Evaluierung des Cores und der Einsatz in kundenspezifischen, auch kommerziellen Anwendungen, ist damit einfach möglich. Zusätzlich forscht und entwickelt das Fraunhofer IMS an anwendungsspezifischen Erweiterungen, beispielsweise für die Bereiche Leistungselektronik, medizinische Anwendungen oder Bildverarbeitung.

Neuestes Ergebnis dieser Entwicklungen ist ein Paket von Beschleunigern für die extrem effiziente Inferenz von neuronalen Netzen. Hierdurch wird der Einsatz von modernen KI-Algorithmen auch auf extrem energiekritischer Hardware, beispielsweise in energieautarken Sensorsystemen, ermöglicht. Das Erweiterungspaket besteht aus den folgenden Komponenten:

- Sammlung von Hardware-Beschleunigern für gängige Aktivierungsfunktionen (AF). Hierzu zählen bspw. tanh, sigmoid, softsign sowie softmax auf Basis der e-funktion.

- Die parallele Ausführung mehrerer Multiplikations- und Addier-Operationen (Multiply-Accumulate für Matrix-Multiplikationen). Aktuell für die Datentypen 16-Bit Integer (2-fach parallel) und 8-Bit Integer (4-fach parallel). Die Erweiterung ersetzt die Standard-ALU und benötigt damit den minimal möglichen Overhead an Hardware bei maximaler Geschwindigkeit durch direkte Integration in die Pipeline des Prozessors.

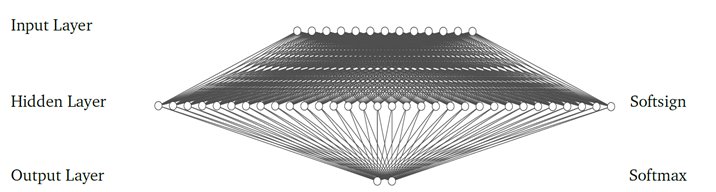

Als Benchmark für die beschriebenen Beschleuniger dient ein Feed-Forward Neuronales-Netz mit 13 Neuronen im Input-Layer, einem Hidden-Layer mit 17 Neuronen sowie zwei Neuronen im Output-Layer. Das Netz stammt aus einer realen Anwendung zur Untersuchung von EKG-Daten auf das Vorhandensein von Vorhofflimmern.

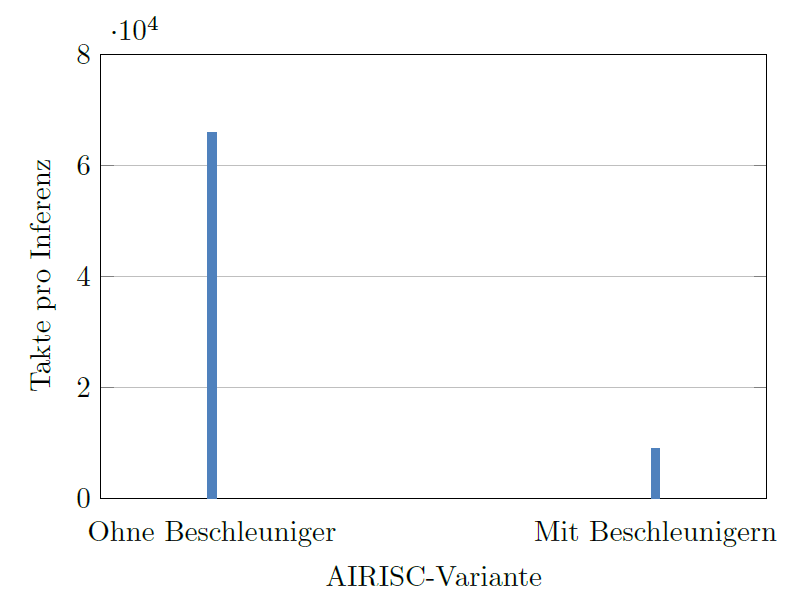

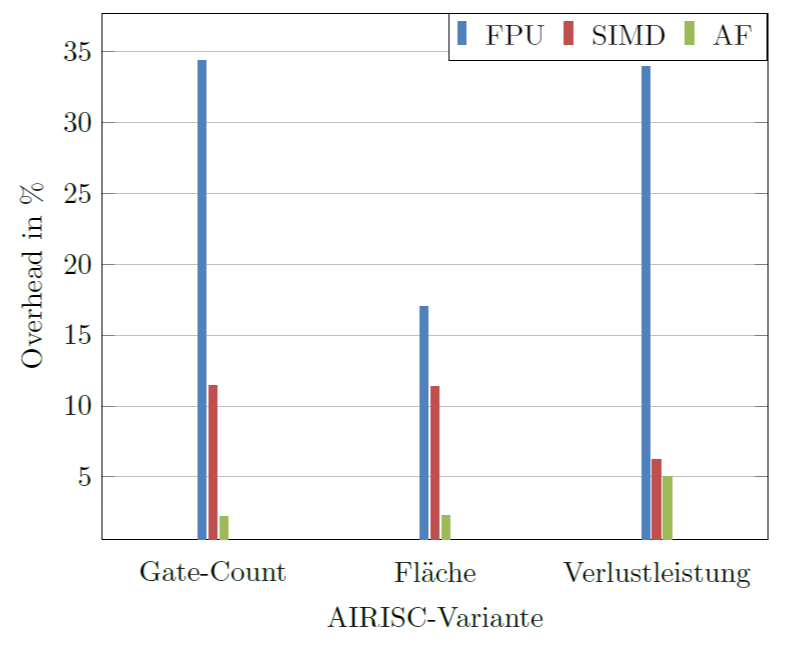

Durch die Verwendung der Hardware-Beschleuniger lässt sich ein Geschwindigkeitsvorteil von mehr als einem Faktor 7 bei der Inferenz des neuronalen Netzes erzielen (Abb. 3). Neben der parallelen Ausführung der Matrix-Multiplikationen wird hier ebenfalls ein großer Anteil an Speicherzugriffen eingespart. Abb. 4 zeigt den Overhead an Hardware, Fläche und Verlustleistung, den die beschriebenen Beschleuniger mit sich bringen. Zusätzlich ist der Bedarf dargestellt, welcher die ebenfalls für den AIRISC verfügbare Hardware-Fließkommaeinheit (FPU) mit sich bringt.

Dem hohen Vorteil hinsichtlich Geschwindigkeit steht ein moderater Overhead an benötigter Hardware gegenüber. Durch die hierdurch mögliche signifikante Reduktion der Betriebsfrequenz kann so ein erheblicher Anteil der benötigten Leistungsaufnahme des Systems eingespart werden. Details wurden beim 5-ten Treffen der Duisburger RISC-V Gruppe präsentiert. Der Vortrag ist über den YouTube Kanal von RISC-V[2] International abrufbar. Die mögliche Energieersparnis durch den Einsatz des entwickelten Chips, insbesondere auch im Vergleich mit Standard-Plattformen, wird im Laufe des Projekts Green ICT @FMD im Detail untersucht.