Fraunhofer IIS – Dieser Tech-Blog untersucht SoC FPGAs, die neben ARM-basierten Prozessorkernen programmierbare Hardwarestrukturen integrieren und als Hardwarebeschleuniger genutzt werden können, um die Energieeffizienz zu verbessern. Der Blog erklärt das Konzept der Hardware-Virtualisierung, bei dem Software-Container Programmierinformationen für verschiedene Hardwarestrukturen enthalten, die bei Bedarf in FPGAs geladen werden. Anhand eines Testdesigns in Form eines neuronalen Netzes wurden verschiedene Implementierungen hinsichtlich ihrer Leistungsfähigkeit und Energieeffizienz bewertet.

Der Schwerpunkt dieses Tech-Blogs liegt auf SoC FPGAs. Darunter werden System-on-a-Chip Lösungen verstanden, die neben häufig auf ARM-Technologie basierenden Prozessorkernen programmierbare Hardwarestrukturen eines FPGA integrieren. Typischerweise kann ein Teil dieser FPGA-Strukturen für die Realisierung von Hardwarebeschleunigern genutzt werden. Diese entlasten die Software, die auf dem integrierten Prozessor ausgeführt werden und führen zu schnelleren Ergebnissen. Es stellt sich die Frage, ob durch den Einsatz von diesen Hardwarestrukturen Energie eingespart werden kann. Der Begriff Hardware Virtualisierung ist im Augenblick noch nicht geläufig. Diese Art von Virtualisierung setzt voraus, dass sich eine Hardware im Betrieb ändern lässt. Im Betrieb partiell rekonfigurierbare FPGAs unterstützen dieses Verfahren gut. Bei dieser Art von Virtualisierung beinhaltet ein Software Container neben Software Komponenten Programmierinformationen für verschiedene Hardwarestrukturen. Diese werden bei Bedarf in ausgewählte Bereiche des FPGAs geladen. Dabei ist zu beachten, dass es sich um keine reine Hardwarelösung handelt. Ein Co-Prozessor benötigt zwingend einen Proxy in Software, der die Hardware mit Daten versorgt und das Ergebnis der Berechnung abholt.

Für die HW-Virtualisierung wird ein Applikationsinterface zum FPGA benötigt. Über dieses API können vom Prozessor Teilbereiche innerhalb des FPGAs programmiert oder Daten an die Hardwarestruktur übergeben und gelesen werden. Weiterhin wird eine Schnittstelle zwischen der Software in dem Container und dem FPGA API genutzt.

Die eigentlichen Applikationen arbeiten in der virtualisierten Containerumgebung des Prozessors. Beim Aufstarten eines Containers holt sich eine Managementsoftware Informationen, ob in einem der partiellen Bereiche im FPGA für die zugehörige HW-Implementierung ausreichend Platz zur Verfügung steht. Wenn dies der Fall ist, wird das HW-Design in das FPGA geladen. Sind nicht ausreichend Ressourcen vorhanden, startet stattdessen eine im Container vorgehaltene Softwarekomponente mit der gleichen Funktionalität.

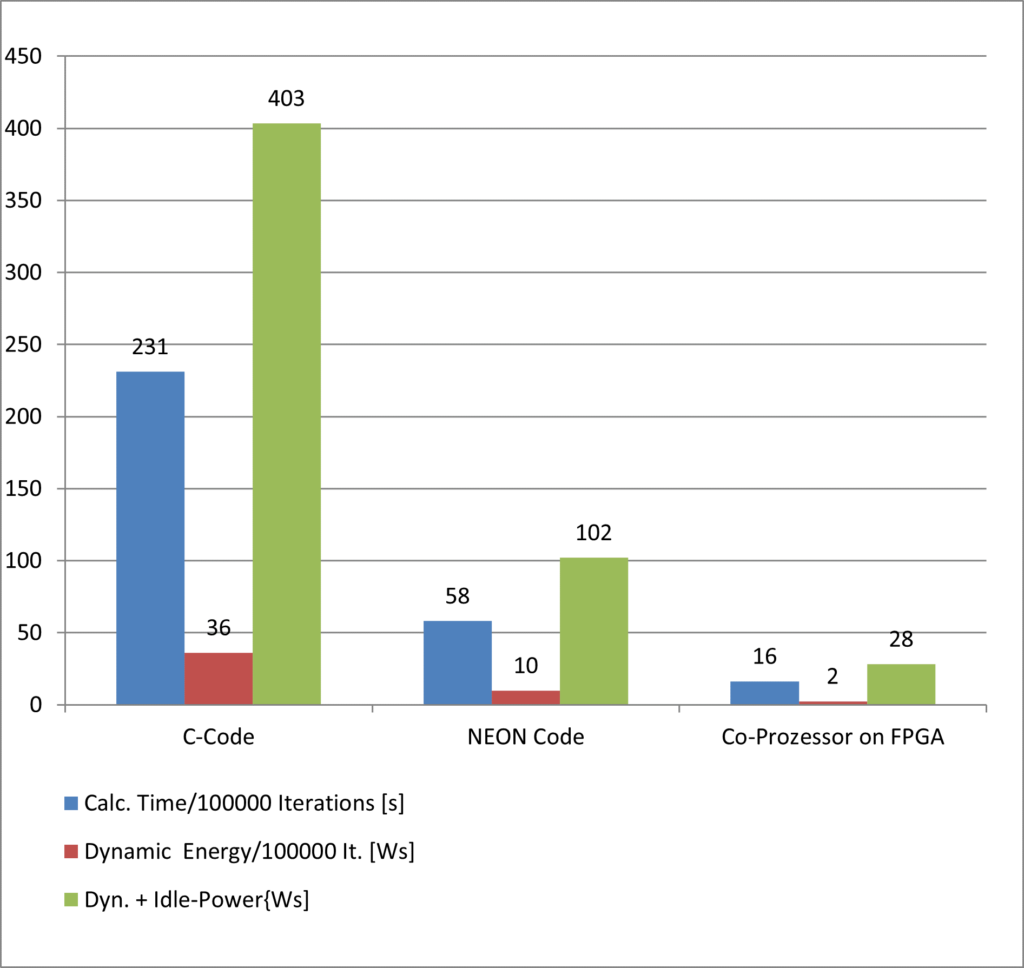

Um die Ergebnisse der HW-Virtualisierung bewerten zu können, entstand ein Testdesign in Form eines Neuronalen Netzes als typischer Vertreter eines Co-Prozessors. Im Anschluss wurden verschiedene Implementierungen auf ihre Leistungsfähigkeit und Energieeffizienz untersucht. Die Ergebnisse finden sich im nachfolgenden Diagramm.

Die ersten beiden Lösungen im Diagramm zeigen zwei reine Softwareimplementierungen des neuronalen Netzes: eine nicht optimierte Version, die in der Programmiersprache C erstellt wurde, und eine zweite Version, die optimierten NEON-Code für ARM-Prozessoren nutzt. Die blauen Balken stellen die Ausführungsgeschwindigkeit dar, die roten Balken die Energieaufnahme für die Ausführung des neuronalen Netzes über 10.000 komplette Durchläufe, und die grünen Balken die Gesamtenergieaufnahme einschließlich der statischen Energieaufnahme für jede Lösung. Bereits der Einsatz von optimiertem C-Code führt zu einer deutlich energieeffizienteren und schnelleren Implementierung. Der Einsatz eines Hardwarebeschleunigers ermöglicht im Vergleich dazu eine zusätzliche dynamische Energieeinsparung um den Faktor 5.