Im Rahmen von Green ICT @ FMD arbeitet das Fraunhofer IAF an der Entwicklung eines Prozesses zur Herstellung von III/V‑Halbleiterschichten auf Si-Substraten zur Minimierung des Arsen-Anteils in Bauelementen. Für die Qualifizierung des Substrattransferprozesses konnten InGaAs Verstärker ICs auf Silizium-Substraten mit ausgezeichneten Höchstfrequenzeigenschaften realisiert werden.

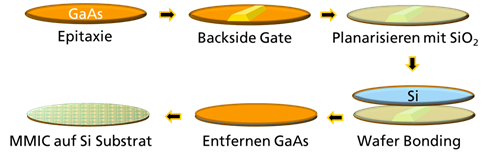

Im Rahmen des Arbeitspaketes „Substratmaterialersatz für III/V-Halbleiter“ wird im Projekt Green ICT @ FMD ein Prozess zur Herstellung von III/V-Halbleiterheterostrukturen auf Si-Substraten zur Minimierung des As-Anteils in Bauelementen entwickelt. Der hierbei durchgeführte Substrattransfer erfolgt mit Hilfe eines auf SiO2-Schichten basierenden Direktbond-Prozesses zwischen dem epitaxierten GaAs-Wafer und einem Hochwiderstands-Si-Substrat. Mittels CMP Prozess wird eine Planarisierung der SiO2-Oberfläche mit einer geringen Oberflächenrauigkeit von < 0.5 nm durchgeführt. Dies ist entscheidend für einen geringen Abstand der Waferoberflächen, der die Bondstärke der Verbindung nach Aktivierung der Oberflächen bestimmt. Nach anfänglichen Abplatzungen der SiO2-Schicht vom GaAs-Wafer konnte durch Optimierung der Vorbehandlung und Abscheideparameter auch hier die für eine weitere Prozessierung notwendige Haftkraft erzielt werden. Derzeit erfolgt die Entfernung des GaAs-Substrates noch basierend auf einem mechanischen Grind-Prozess in Kombination mit selektivem nasschemischen Ätzschritten. Dieses Verfahren soll im weiteren Projektverlauf in Hinblick auf ein Recycling des GaAs-Substrates weiterentwickelt werden. Die Dicke der untersuchten Bauelementheterostruktur betrug 100 nm.

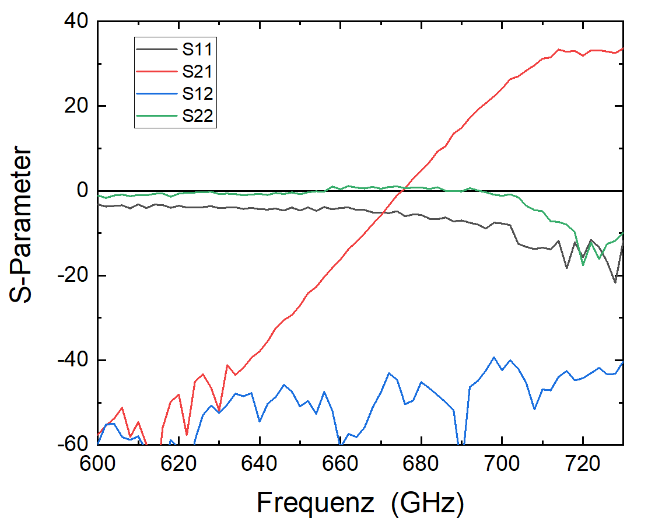

Zur Evaluierung der III/V-Heterostrukturen auf Si wurden Höchstfrequenzschaltungen basierend auf 20 nm InGaAs HEMT Transistoren hergestellt. Es traten innerhalb der Prozessierung keine Ablösungen von Schichten auf. Erstmals zeigten auf Silizium realisierten Schaltungen sogar gegenüber denen auf GaAs-Substraten überlegene Hochfrequenzeigenschaften. Dies wird auf das verbesserte Abschnürverhalten der Transistoren, bedingt durch die rückseitige SiO2-Schicht, zurückgeführt. Hierdurch werden unerwünschte Kurzkanaleffekte aufgrund der geringen Gatelänge von 20 nm unterdrückt.

Für einen Ersatz der GaAs-Substrat Prozesse in der Mikroelektronik ist weiterhin die Entwicklung eines Si-Substrat-Rückseiten-Prozesses erforderlich. Dieser beinhaltet das Aufkleben der Wafer auf Träger, das Abdünnen der Si-Wafer auf 50 bzw. 25 µm Dicke, das Ätzen von Substrat-Vias ins Silizium, die Metallisierung der Vias und der Waferrückseite sowie das Entfernen der Goldmetallisierung in den Sägegräben. Entsprechende Prozesse für Silizium-Substrate stehen mittlerweile am IAF zur Verfügung. Für die Entwicklung der Substratdurchkontaktierungen basierend auf einem Bosch Trockenätzprozess stellten sich insbesondere Aufladungseffekte, verursacht durch die SiO2 Bondschicht, als eine Herausforderung heraus.