»GREEN ICT @ FMD« – KOMPETENZZENTRUM FÜR ÖKOLOGISCH NACHHALTIGE IKT

# Ressourceneffiziente Radar-Signalverarbeitung auf Mikrocontrollern

Ein Whitepaper von "HUB 1 – Sensor-Edge-Cloud-Systeme"

Michel Sonntag (Fraunhofer FHR), Michael Gräf (Fraunhofer FHR), Sabine Gütgemann (Fraunhofer FHR),

Christian Krebs (Fraunhofer FHR)

Dieses Whitepaper ist Teil des Projekts „Green ICT @ FMD“ – Kompetenzzentrum für ökologisch nachhaltige Informations- und Kommunikationstechnik. Das Projekt wird von der Forschungsfabrik Mikroelektronik Deutschland (FMD) durchgeführt und vom Bundesministerium für Forschung, Technologie und Raumfahrt gefördert.

## Kompetenzzentrum »Green ICT @ FMD«

c/o Forschungsfabrik Mikroelektronik Deutschland FMD

Anna-Louisa-Karsch-Str. 2

10178 Berlin, Germany

Ansprechperson

Sabine Gütgemann, sabine.guetgemann@fhr.fraunhofer.de

[www.greenict.de](http://www.greenict.de)

[www.forschungsfabrik-mikroelektronik.de](http://www.forschungsfabrik-mikroelektronik.de)

Veröffentlicht:

08.12.2025

© Fraunhofer-Verbund Mikroelektronik

# 1. Einführung

Ressourceneffiziente Informations- und Kommunikationstechnik (Green ICT) erfordert neuartige Systementwürfe, die Energie- und Materialaufwand über den gesamten Lebenszyklus senken, ohne die funktionale Leistungsfähigkeit zu kompromittieren. Radarsysteme stellen dabei eine besondere Herausforderung dar: Sie basieren typischerweise auf FFT-zentrierten Signalverarbeitungsketten mit hohen Anforderungen an Rechen- und Speicherressourcen, was häufig FPGAs oder GPUs nahelegt. Die daraus resultierende Leistungsaufnahme ist jedoch in mobilen, verteilten oder skalierten Sensornetzen ein kritischer Faktor und wirkt sich zudem auf Ökobilanzen aus. Vor diesem Hintergrund adressiert diese Arbeit die Verlagerung wesentlicher Verarbeitungsschritte auf Mikrocontroller-(μC)-Plattformen und die Gestaltung verteilter Sensor-Edge-Architekturen.

Im Bereich der Spektralanalyse ist bekannt, dass die nominelle Frequenzauflösung der FFT mit der Blockgröße skaliert und dass Fensterung, Leakage und Schätzvarianz die praktische Genauigkeit limitieren [1]. Größere FFTs verbessern die Auflösung, erhöhen aber die Rechenlast und damit die Energieaufnahme. Demgegenüber erlauben feinauflösende Schätzer auf Basis von Peak-Interpolation (parabolisch) eine sub-Bin-Genauigkeit bei kleineren Blockgrößen, sofern SNR, Fensterung und Modellannahmen konsistent sind [2]. Parallel dazu bieten zeitinterleavte ADCs eine Möglichkeit, die effektive Abtastrate zu steigern; sie erfordern jedoch eine Kalibrierung von Gain-, Offset- und Timing-Skews sowie ein jitterarmes Takt- und Trigger-Design, um Phasenkohärenz und SNR sicherzustellen [5].

Diese Arbeit stellt einen radarzentrierten Demonstrator vor, der

1. ein μC-basiertes Backend für bis zu vier phasenkohärenten Kanälen (80 GHz),

2. zur Laufzeit zwischen Independent- (1-4 Kanäle) und Interleaved-Betrieb (1-2 Kanäle, erhöhte Abtastrate) umschalten kann,

3. eine FFT-nahe Peak-Interpolation integriert, um die FFT-Blockgröße zu reduzieren bei gleichbleibender Messqualität, und

4. die verteilte Aufgabenaufteilung zwischen Sensor und Edge demonstriert.

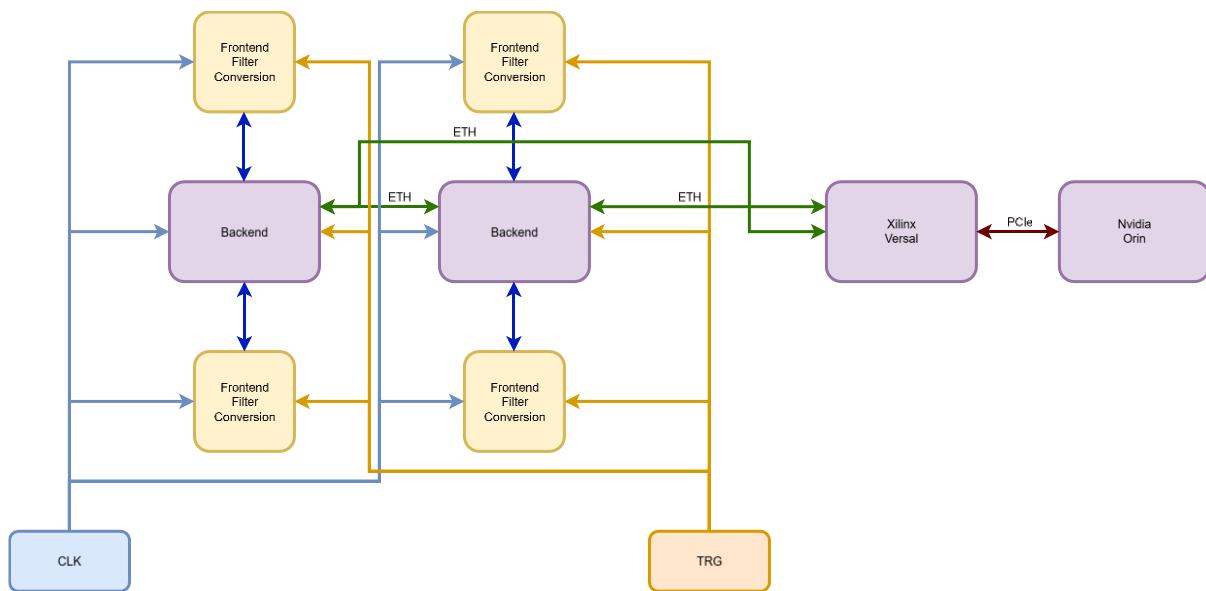

Die Hardware ist modular aufgebaut (Frontend, Filter/Conversion, Backend) und unterstützt selektives Power-Gating, um Teillast- und Ereignisbetrieb effizient abzudecken. Kritische Aspekte wie phasenkohärente Erfassung über mehrere ADCs/Controller, externes Block-Triggering und Clock-/Jitter-Management werden adressiert.

## 1.1 Problemstellung

Wie lässt sich die zentrale Radar-Signalverarbeitung von FPGA-/GPU-Plattformen auf μC-Architekturen verlagern, sodass (a) die Energieaufnahme des Gesamtsystems messbar sinkt, (b) die Messqualität (Frequenz-/Entfernungsschätzung) erhalten bleibt und (c) die Architektur für verteilte Sensor-Edge-Szenarien skalierbar ist? Dabei sind die folgenden Randbedingungen maßgeblich:

- Begrenzte Rechen-/Speicherressourcen der μC-Plattform im Vergleich zu FPGA/GPU.

- Anforderungen an Phasenkohärenz über Mehrkanal- und Mehrcontroller-Strukturen (Trigger/Clock/Jitter/Skew).

- Betriebsmodi- und Bandbreitenflexibilität (Independent vs. Interleaved) mit zur Laufzeit veränderbaren ADC-Parametern.

- Lebenszyklus- und Ökobilanzperspektive

## 1.2 Geltungsbereich und Abgrenzung

Der Fokus liegt auf FMCW Nahbereichsanwendungen mit Anforderungen an Distanzschätzung (Zielreichweite, Bandbreite und Update-Rate einstellbar). Themen wie MIMO-Winkelmessung, komplexe Mehrziel-Tracking-Algorithmen oder Safety-zertifizierte Implementierungen sind außerhalb des unmittelbaren Scopes, werden jedoch im Ausblick adressiert. Die Edge-Komponente dient der Visualisierung/Feature-Aggregation. Cloud-Backend Strukturen werden an dieser Stelle nicht betrachtet.

## 2. Systemarchitektur

Dieses Kapitel beschreibt die Architektur des radarbasierten Demonstrators entlang der kompletten Signalkette: vom Frontend (80 GHz) über Filter/Conversion und das Mikrocontroller-Backend in Master/Slave-Konfiguration bis zu den Edge-Cloud Komponenten (Xilinx Versal, Nvidia Orin). Im Fokus stehen eine ressourceneffiziente, modulare Hardware, phasenkohärente Mehrkanal-Erfassung, konfigurierbare ADC-Betriebsarten (Independent/Interleaved) sowie eine Firmware, die FFT-basierte Signalverarbeitung mit Peak-Interpolation energieeffizient auf einer µC-Plattform umsetzt. Designentscheidungen sind auf Energieeffizienz, Messqualität und Adaptivität für unterschiedliche Anwendungsszenarien ausgelegt.

Abbildung 1 Vereinfachte schematische Darstellung Konzept FHR

### 2.1 Gesamtübersicht und Designziele

Der Demonstrator verfolgt das Ziel, eine FPGA-basierte Referenzlösung durch ein µController-Backend zu ersetzen und dabei die Systemleistung signifikant zu senken, ohne die Messqualität zu kompromittieren. Kernprinzipien sind:

- **Modularität:** Frontend, Filter/Conversion, Backend und Adapter werden als eigenständige, steckbare Module ausgeführt. Das erleichtert das Zuschalten/Abschalten von Baugruppen, isolierte Messungen einzelner Pfade und die Wiederverwendung in künftigen Systemen.

- **Energieeffizienz:** Selektives Power-Gating (u. a. Slave-µC und Peripherie) und teillastoptimierte Betriebsstrategien (Duty-Cycling, Feature-First-Streaming) reduzieren die mittlere Leistungsaufnahme.

- **Phasenkohärenz:** Externes, blockweises Triggering und kohärente Clock-Distribution sichern identische Phasenlage in Mehrkanal- und Mehrcontroller-Betrieb [6].

- **Flexibilität:** ADC-Modi sind zur Laufzeit umschaltbar (Independent 1–4 Kanäle; Interleaved 1–2 Kanäle mit erhöhter effektiver Abtastrate). Auflösung und Samplingrate werden Szenario-basiert angepasst.

- **Edge-Integration:** Einbindung in ein System mit unterschiedlichen Systemkomponenten zur intelligenten Verteilung der Rechenlast.

## 2.2 Hardwarearchitektur

Das Backend besteht aus zwei identischen Mikrocontroller-Boards (z. B. STM32H735, Cortex-M7 mit FPU und DSP-Instruktionen), die in einer Master/Slave-Topologie betrieben werden. Beide Boards führen dieselbe Firmware aus; die Rollenzuweisung erfolgt deterministisch im Boot-Prozess (Boot-Strapping). Der Master kann den Slave-Controller und ausgewählte Peripherie über Power-Switches hart abschalten oder in definierte Sleep-Zustände versetzen. Dieses Power-Gating ist ein zentraler Hebel für Teillast- und Ereignisbetrieb. Die Plattform stellt vier ADC-Kanäle bereit. Im Independent-Mode werden 1–4 Kanäle parallel mit Standard-Abtastrate betrieben. Im Interleaved-Mode werden 1–2 Kanäle mit verdoppelter effektiver Abtastrate realisiert, indem zwei ADC-Kerne alternierend dasselbe Eingangssignal abtasten. Für den Interleaved-Betrieb ist eine Single-Ended-Einspeisung erforderlich; die Differential-to-Single-Ended-Conversion ist auf der Filterplatine integriert. Die Zielkonfiguration deckt 16-Bit-Auflösung und Worst-Case-Samplingraten bis 7,2 MSps/Kanal ab, weitere Raten/Bit-Tiefen sind zur Laufzeit konfigurierbar.

Zur Sicherung der Phasenkohärenz werden beide µC-ADCs extern und blockweise getriggert (Master-GPIO). Der Taktpfad ist kohärent ausgeführt; Längen, Impedanzen und Verteilungselemente werden so gestaltet, dass Kanal- und Controller-Skews reproduzierbar klein bleiben. Eigene Evaluationsboards dienen der Messung und Optimierung von Trigger-Jitter und Kanal-Skews. Ein Block-Trigger (statt Sample-Trigger) senkt Interrupt-Last und erhöht die Robustheit gegenüber Jitter.

*Tabelle 1 System Eigenschaften*

| Aspekt            | Status                                                     |

|-------------------|------------------------------------------------------------|

| Radarprinzip      | FMCW                                                       |

| Frontend Frequenz | 80 GHz                                                     |

| Bandbreite        | 25 GHz                                                     |

| Chirprate         | 102,4 µs                                                   |

| Kanäle            | 1 – 4                                                      |

| ADC Modi          | Independent (1-4 Kanäle), Interleaved (1-2 Kanäle)         |

| ADC Auflösung     | 10 – 16 Bit                                                |

| ADC Abtastrate    | 3,6 – 11 MSps                                              |

| Triggerung        | Intern oder extern                                         |

| Power Management  | Selektives Power-Gating                                    |

| Edge Integration  | Rechenlast über Xilinx Versal oder Nvidia Orin verteilebar |

### 3. Methoden und Implementierung

Dieses Kapitel beschreibt die konkrete Umsetzung der ressourceneffizienten Radar-Signalverarbeitung auf einer Mikrocontrollerplattform. Der Fokus liegt auf (i) einer FFT-nahen Frequenzschätzung mit Peak-Interpolation zur Reduktion der Rechenlast, (ii) phasenkohärenter Mehrkanal-Erfassung über zwei Controller, (iii) flexiblen ADC-Betriebsarten (Independent/Interleaved) einschließlich Laufzeitumschaltung sowie (iv) Firmware- und Energie-Management-Strategien zur Senkung der mittleren Leistungsaufnahme. Ergänzend wird die Einbindung in Edge-Komponenten für Visualisierung und anwendungsnahe Demos beschrieben.

#### 3.1 Signalverarbeitungsansatz: FFT-verträgliche Peak-Interpolation

Radarsensoren nutzen typischerweise FFT-basierte Ketten für Distanz- und Geschwindigkeitsabschätzungen. Die nominale Frequenzauflösung steigt mit der FFT-Länge, was Rechen- und Speicherbedarf treibt. Um auf µC-Strukturen eine äquivalente Messqualität bei deutlich reduzierter Rechenlast zu erzielen, setzen wir auf einen zweistufigen Ansatz:

- Vorverarbeitung und Fensterung: Die Rohdaten werden mit bewährten Fenstern (z. B. Hamming) aufbereitet, um Leakage zu kontrollieren und die Varianz der Schätzer zu senken [1]. Die Fensterwahl bleibt konfigurierbar, sodass sich SNR- und Szenario-anforderungen abbilden lassen.

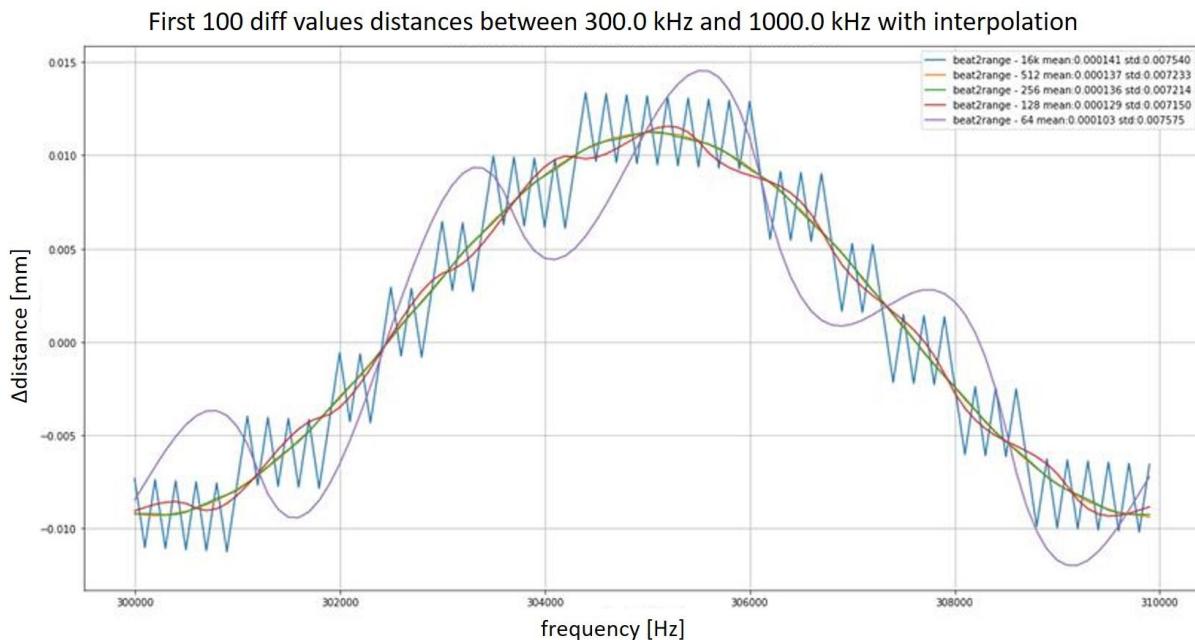

- Peak-Interpolation im Frequenzraum: Statt die FFT-Länge zu erhöhen, wird der stärkste Spektralanteil per parabolischer Interpolation (PI) sub-Bin-genau geschätzt. Simulationen mit repräsentativen SNRs zeigen eine nahezu kontinuierliche Frequenzschätzung bei kleineren FFT-Größen (Abbildung 2). Damit lässt sich Rechen- und Speicherlast senken, ohne die für Distanzschatzung relevante Genauigkeit zu kompromittieren [2, 3].

Abbildung 2 Simulationsergebnisse parabolische Interpolation gegenüber 16k FFT (FPGA); (blau) 16k FFT, (orange) 512 FFT mit PI, (grün) 256 FFT mit PI, (rot) 128 FFT mit PI, (lila) 64 FFT mit PI

Die Implementierung nutzt CMSIS-DSP und µC-spezifische DSP-Instruktionen (Cortex-M7, FPU) [7]. Datenpfade und Puffergrößen sind so gewählt, dass Cache-Trefferraten maximiert, Kopieroperationen minimiert und DMA-Transfers effizient genutzt werden. Der gesamte Kettenaufbau bleibt modular, um spätere Erweiterungen (z. B. zusätzliche Merkmale wie Phasendifferenzen) mit begrenzten Anpassungen zu integrieren.

### **3.2 Phasenkohärente Erfassung und Trigger-/Clock-Konzept**

Für Mehrkanal- und Mehrcontroller-Betrieb ist Phasenkohärenz eine Grundvoraussetzung, damit Master und Slave bei identischer Szene äquivalente Ergebnisse liefern. Das Konzept umfasst:

- Externes Block-Triggering: Ein Master-GPIO triggert beide µC-ADCs blockweise. Block- statt Sample-Trigger reduziert Interrupt-Last und Jitter-Sensitivität.

- Kohärente Clock-Distribution: Taktpfade, Leitungslängen und Impedanzen sind symmetriert ausgeführt. Evaluationsboards dienen zur Messung und Optimierung von Trigger-Jitter und Kanal-Skews.

- Reproduzierbarkeit: Trigger- und Clock-Pfade werden messtechnisch charakterisiert; Kalibrierungsroutinen (Offset/Gain/Timing) sind für den Interleaved-Betrieb vorgesehen.

### **3.3 ADC-Betriebsarten und Laufzeitanpassung**

Zur Abdeckung unterschiedlicher Messanforderungen sowie für ein günstiges Energie-Genauigkeits-Verhältnis unterstützen die ADCs zwei Modi:

- Independent-Mode: 1–4 Kanäle bei Standardabtastraten, differenzielle Einspeisung möglich.

- Interleaved-Mode: 1–2 Kanäle mit verdoppelter effektiver Abtastrate durch alternierende Abtastung zweier ADC-Kerne. Die dafür nötige Single-Ended-Einspeisung wird auf der Filterplatine per Differential-to-Single-Ended-Conversion bereitgestellt.

Auflösung (z. B. 16 Bit) und Abtastraten (Worst-Case bis 7,2 MSps/Kanal) sind zur Laufzeit konfigurierbar. Die Umschaltung wird über eine einheitliche Firmware-API realisiert und erlaubt, auf Szenariowechsel (z. B. höhere Bandbreite, schnellere Updates) ohne Neustart zu reagieren.

### **3.4 Firmware-Architektur und Energie-Management**

Beide µC-Boards (z. B. STM32H735, Cortex-M7) laufen mit identischer Firmware. Die Rollenzuweisung (Master/Slave) erfolgt deterministisch im Boot-Prozess. Kernelemente:

- Power-Gating und Duty-Cycling: Der Master kann den Slave-µC und ausgewählte Peripherie (z. B. Frontends, Filter/Conversion) hart abschalten oder in definierte Sleep-Zustände versetzen. Ereignis- und Teillastbetrieb senken die mittlere Leistungsaufnahme signifikant.

- Feature-First-Streaming: Nur relevante Merkmale (z. B. Peaks, Entfernung, Phasen) werden priorisiert übertragen; Rohdatenstreaming bleibt optional für Diagnostik und Validierung.

- Modulare Software: Die Pipeline ist in wiederverwendbare C-Module gegliedert (Er-fassung, Vorverarbeitung, FFT, Interpolation, Merkmalsextraktion, Protokolle). Das beschleunigt Tests, erleichtert die Portierung und ermöglicht gezielte Laufzeitmes-sungen einzelner Stufen.

### **3.5 Edge-Integration und Visualisierung**

Die sensornahen Vorverarbeitung findet auf dem µC statt. Ein Raspberry Pi übernimmt 2D/3D-Visualisierung (Phase, Magnitude, Distanz) für Demos und Kundengespräche. Für komplexere Workloads (z. B. Tracking, Filter höherer Ordnung) ist eine optionale Edge-Beschleunigung (z. B. Xilinx Versal, NVIDIA Orin) vorbereitet. Ziel ist eine balancierte Sensor-Edge-Aufteilung: Netzwerklast reduzieren, Latenzen kontrollieren, Energie gesamtsystemisch senken.

## 4. Ergebnisse

### 4.1 Rechen- und Messqualität

Die Simulationen belegen: Kleinere FFTs in Kombination mit parabolischer Peak-Interpolation liefern eine nahezu kontinuierliche Frequenzschätzung bei konsistenter Fensterung und ausreichendem SNR [2, 3, 4]. In der Praxis bedeutet dies, dass Distanzschätzergebnisse der µC-Kette zur FPGA-Referenzlösung äquivalent ausfallen können, während Rechenlast und Speicherzugriffe sinken. Der Ansatz ist robust gegenüber moderaten Jitter-/Skew-Variationen, verlangt aber ein sauberes Clock-/Trigger-Design.

### 4.2 Energieaufnahme und Einsparpotenzial

Messungen unter Volllast (alle Komponenten aktiv; 16-Bit, 7,2 MSps) zeigen folgende Leistungsaufnahme:

Tabelle 2 Leistungsaufnahme pro Baugruppe

| Baugruppe         | Anzahl | Leistungsaufnahme Baugruppe [W] | Leistungsaufnahme gesamt [W] |

|-------------------|--------|---------------------------------|------------------------------|

| Backend           | 2      | 1,944                           | 3,888                        |

| Filter/Conversion | 4      | 1,022                           | 4,088                        |

| Frontend Adapter  | 4      | 0,564                           | 2,256                        |

| Frontend          | 4      | 0,804                           | 3,216                        |

| System            |        |                                 | 13,448                       |

Gegenüber einem 4-Kanal-FPGA-Referenzsystem ergibt sich im Worst-Case eine Leistungseinsparung von **24,577%**. In realistischen Teillastszenarien (sensorseitige Vorverarbeitung, reduziertes Streaming, Duty-Cycling) ist eine zusätzliche Senkung der mittleren Energieaufnahme zu erwarten, da Power-Gating und Block-Triggering ihre Wirkung stärker entfalten.

## 5. Ökobilanzierung

Ziel dieses Kapitels ist eine belastbare, lebenszyklusbezogene Bewertung der Klimawirkung des µC-basierten Radardemonstrators. Grundlage der Herstellungsphase sind die aus der Stückliste abgeleiteten Ergebnisse gemäß den Rahmenvorgaben der ISO 14040 [9]. Die Nutzungsphase wird über ein konkretes, plausibles Lastprofil modelliert und mit einem FPGA-Referenzsystem verglichen. End-of-Life-Effekte werden qualitativ betrachtet, da verifizierte Datensätze hierfür noch nicht vorliegen.

### 5.1 Herstellungsphase: Ergebnisse und Hot-Spots

Die Analyse der Stückliste zeigt, dass Leiterplattenfertigung (PCB) und integrierte Logik den größten Anteil an den Herstellungswirkungen haben. Auf Systemebene (4x Frontend, 4x Adapter, 4x Filter/Conversion, 2x Backend) ergibt sich folgender Befund:

Tabelle 3 CO<sub>2</sub>e pro Baugruppe

| Baugruppe         | Anzahl | Herstellung<br>[kg CO <sub>2</sub> e] | Anteil am Sys-<br>tem<br>[%] |

|-------------------|--------|---------------------------------------|------------------------------|

| Backend           | 2      | 13,381                                | 32,6                         |

| Filter/Conversion | 4      | 15,624                                | 38,1                         |

| Frontend Adapter  | 4      | 8,925                                 | 21,8                         |

| Frontend          | 4      | 3,068                                 | 7,5                          |

| System            |        | 40,994                                | 100                          |

Über alle Module hinweg entfällt der größte Anteil auf PCB-Prozesse und Logik/Prozessoren (zusammen rund 85%). Aggregiert nach Bauteilklassen zeigt sich: PCB ≈ 18,43 kg CO<sub>2</sub>e (≈45%), CMOS-Logik ≈ 16,62 kg (≈41%), MPU ≈ 4,59 kg (≈11%); Transistoren und Assembly sind nachrangig. Der Hebel für weitere Reduktionen liegt damit primär in PCB-Design und Fertigung (Fläche, Lagenzahl, Material, Ausnutzung) sowie in der Funktionsintegration und Konsolidierung von Logik/MPU.

## 5.2 Nutzungsphase: konkretes Lastprofil und mittlere Leistungsaufnahme

Für den Betrieb wurde ein praxisnahes, ereignisorientiertes Profil definiert, das Teillast und Standby-Phasen gezielt ausnutzt. Die Modellierung stützt sich auf die Anforderungen gemäß ISO 14044 [10]. Als Referenz dient die gemessene Volllast von 13,448 W (alle Baugruppen aktiv, 16 Bit, 7,2 MSps). Die vier Zustände und deren relative Leistungsniveaus sind:

- Vollbetrieb (30% der Zeit): 100% der Referenzleistung.

- Teillast A – reduzierte Rate/auflösungsoptimiert (40%): 60% der Referenzleistung.

- Teillast B – „idle-armed“ (20%): 30% der Referenzleistung.

- Standby/Sleep (10%): 10% der Referenzleistung.

Aus diesen Annahmen ergibt sich eine mittlere Leistungsaufnahme des μC-Systems von 8,20 W. Das FPGA-Referenzsystem wird gemäß Messvergleich mit 24,577% Mehrleistung angesetzt; damit liegt dessen mittlere Leistung bei 10,22 W.

## 5.3 Jahresverbrauch, Klimawirkung und Vergleich zum FPGA

Für einen industriellen Einsatz mit 6.000 Betriebsstunden pro Jahr resultieren daraus folgende Energiemengen. Zur Umrechnung in Treibhausgasemissionen wird ein Strom-Emissionsfaktor von 0,40 kg CO<sub>2</sub>e/kWh verwendet, basierend auf Berichten des Umweltbundesamts [11].

Tabelle 4 Vergleich μC Demonstrator zu Referenzsystem

| System          | Mittlere Leistung [W] | Jahresarbeit [kWh/a] | Nutzung GWP<br>[kg CO <sub>2</sub> e/a] |

|-----------------|-----------------------|----------------------|-----------------------------------------|

| μC-Demonstrator | 8,20                  | 49,22                | 19,69                                   |

|               |       |       |       |

|---------------|-------|-------|-------|

| FPGA-Referenz | 10,22 | 61,32 | 24,53 |

| Differenz     | 2,02  | 12,10 | 4,84  |

Damit vermeidet das µC-System im genannten Nutzungsprofil pro Jahr rund 12,1 kWh bzw. 4,84 kg CO<sub>2</sub>e gegenüber der FPGA-Referenz. Bei stärkerer Auslastung (mehr aktive Zeit) wächst die Einsparung proportional; bei einem erneuerbaren Strommix sinkt die absolute Klimawirkung, das Verhältnis der beiden Systeme bleibt jedoch gleich.

#### 5.4 Lebenszyklusbewertung, „Carbon Payback“ und Interpretation

Die Herstellungswirkung des µC-Systems beträgt 40,99 kg CO<sub>2</sub>e. Setzt man die jährliche Nutzungseinsparung von 4,84 kg CO<sub>2</sub>e (gegenüber FPGA) an, ergibt sich ein CO<sub>2</sub>-„Payback“ von etwa 8,5 Jahren, wenn man die Herstellung des Referenzsystems ausklammert. Die Bewertung basiert auf ISO 14040 und ISO 14044 zur Klimawirkung des Lebenszyklus [9, 10], ergänzt durch Emissionsdaten aus UBA-Berichten [11]. Liegt der Strommix höher (z. B. 0,60 kg CO<sub>2</sub>e/kWh) oder die Betriebszeit bei 8.000 h/a, verkürzt sich der Payback auf etwa 5,5–6,5 Jahre; bei sehr CO<sub>2</sub>-armem Strom (0,25 kg CO<sub>2</sub>e/kWh) verlängert er sich entsprechend. Über 10 Jahre Einsatzdauer summieren sich die Nutzungseinsparungen im Basiszenario auf rund 48 kg CO<sub>2</sub>e; die Netto-Bilanz fällt damit zugunsten des µC-Systems aus. Eine vollständige Gegenüberstellung der Herstellungswirkungen beider Alternativen (µC vs. FPGA) ist geplant, sobald belastbare PCF-Daten der Referenz vorliegen; erfahrungsgemäß spricht die geringere Logik-/Peripheriedichte des µC-Ansatzes für zusätzliche Vorteile in der Herstellung.

#### 5.5 Schlussfolgerungen und Maßnahmen

Die Ökobilanz zeigt drei Kernaussagen: Erstens verschieben sich die Hot-Spots klar in Richtung PCB und integrierte Logik, womit Designentscheidungen auf diesen Ebenen besonders wirksam sind. Zweitens realisiert das µC-System im realistischen Teillast-Betrieb signifikante Nutzungseinsparungen gegenüber der FPGA-Referenz; diese sind der zentrale Treiber für die Lebenszyklusvorteile. Drittens beschleunigt ein striktes Energiemanagement (Duty-Cycling, Laufzeitumschaltung der ADC-Modi, selektives Abschalten ganzer Baugruppen) den „Carbon Payback“ messbar. Für die nächste Ausbaustufe empfehlen sich PCB-Optimierungen (Fläche/Lagenzahl), Funktionsintegration in Logik/MPU sowie die Aufnahme standort- und kundenspezifischer Strommix-Szenarien in die Bilanz, um projektspezifische Aussagen zur Amortisationszeit noch präziser zu treffen.

### 6. Diskussion

Der Demonstrator zeigt, dass sich zentrale Schritte der Radar-Signalverarbeitung von FPGA-Plattformen auf eine Mikrocontroller-Architektur verlagern lassen, ohne die Messqualität zu beeinträchtigen. Kern dafür ist die Kombination aus konsequenter Fensterung und einer FFT-nahen Peak-Interpolation, die bei kleineren FFT-Blockgrößen eine sub-Bin-genaue Frequenzschätzung liefert. Simulationen und erste Auswertungen belegen, dass die Distanzschätzung damit zur FPGA-Referenz äquivalent ausfallen kann, wenn SNR, Fensterwahl und das Takt-/Trigger-Design sauber ausgeführt sind. In der Praxis haben sich phasenohärentes Block-Triggering und eine kohärente Clock-Distribution als wirkungsvolle Mittel erwiesen, um Kanal-Skews und Jitter zu beherrschen. Für den Interleaved-Betrieb bleibt eine sorgfältige Kalibrierung von Gain, Offset und Timing-Skew unerlässlich.

Aus Systemperspektive addiert sich die technische Strategie zu einem messbaren Energieeffekt: Gegenüber einer funktional äquivalenten FPGA-Lösung liegt die Leistungsaufnahme des µC-Systems selbst im Worst-Case um 24,577% niedriger. Unter einem realistischen, ereignisorientierten Nutzungsprofil (30% Vollbetrieb, 40% Teillast mit reduzierter Rate, 20% idle-armed, 10% Standby) ergibt sich eine mittlere

Leistungsaufnahme von 8,20 W für das µC-System gegenüber 10,22 W für die Referenz. Über 6.000 Betriebsstunden pro Jahr entspricht das 49,22 kWh gegenüber 61,32 kWh sowie einer jährlichen Klimawirkung von 19,69 kg CO<sub>2</sub>e gegenüber 24,53 kg CO<sub>2</sub>e (EF Strom 0,40 kg/kWh). Die Einsparung von rund 12,1 kWh bzw. 4,84 kg CO<sub>2</sub>e pro Jahr ist substantiell und skaliert mit höherer Auslastung; bei CO<sub>2</sub>-ärmeren Strommixen sinken die absoluten Emissionen, die Relation zwischen den Systemen bleibt bestehen.

Mit Blick auf den Lebenszyklus ist die Herstellungswirkung des µC-Systems (40,99 kg CO<sub>2</sub>e) klar durch Leiterplattenfertigung und integrierte Logik/MPU geprägt; zusammen verursachen sie rund 85% der Herstellungsemissionen. Die Modularität des Aufbaus (Frontend, Adapter, Filter/Conversion, Backend) ist hier ein strategischer Vorteil: Sie erhöht Reparierbarkeit und Wiederverwendbarkeit und ermöglicht Upgrades einzelner Baugruppen, statt komplette Systeme zu ersetzen. Unter dem beschriebenen Nutzungsprofil liegt der „Carbon Payback“ gegenüber der FPGA-Nutzungsemissionen bei etwa 8,5 Jahren; mit längeren Betriebszeiten oder CO<sub>2</sub>-intensiverem Strommix verkürzt er sich entsprechend, mit sehr CO<sub>2</sub>-armem Strommix verlängert er sich. Die vollständige Gegenüberstellung der Herstellungswirkung beider Systemalternativen ist als nächster Schritt vorgesehen; erfahrungsgemäß spricht der geringere Silizium- und Peripheriebedarf des µC-Ansatzes für weitere Vorteile.

Technische Grenzen bleiben: Die Interpolation ist SNR- und Leakage-sensitiv; Fensterwahl und Datenvorberarbeitung sind entscheidend. Interleaved-Sampling erhöht die effektive Rate, fordert aber Kalibrierdisziplin. Speicher- und Cache-Größen auf der µC-Plattform verlangen effiziente DMA- und Buffering-Strategien. Für hochkanalige MIMO-Winkelabschätzung und komplexes Mehrziel-Tracking ist ein hybrider Ansatz sinnvoll: Sensorseitige Feature-Extraktion auf dem µC, rechenintensive Schritte auf Edge-Beschleunigern (z. B. Versal, Orin). Gerade diese Verteilung ist im Sinne von Green ICT vorteilhaft, weil sie Netzwerklast, Latenz und Energie gesamtsystemisch balanciert.

In Summe liefert der Demonstrator drei robuste Erkenntnisse: Erstens ist die µC-Architektur mit Peak-Interpolation technisch tragfähig und energieeffizient. Zweitens entstehen ökologische Vorteile sowohl im Betrieb als auch perspektivisch in der Herstellung durch Modularität und Funktionsintegration. Drittens hängt die reale Wirkung stark von Betriebsprofil und Energiemanagement ab – konsequentes Power-Gating, Laufzeitumschaltung von ADC-Parametern und Feature-First-Streaming sind dabei zentrale Hebel.

## 7. Fazit und Ausblick

Die vorliegende Arbeit belegt, dass ein µC-basiertes Backend die zentrale Radar-Signalverarbeitung mit signifikant geringerer Energieaufnahme bereitstellen kann, ohne die Messqualität gegenüber einer FPGA-Referenz zu kompromittieren. Möglich wird dies durch eine FFT-kompatible Peak-Interpolation, ein phasenkonkärentes Mehrkanal-Konzept und ein strenges Energie- und Laufzeitmanagement, das Teillast- und Ereignisbetrieb gezielt adressiert. Ökobilanziell zeigt das System unter realistischen Nutzungsprofilen klare Vorteile in der Nutzung; mit weiteren Designmaßnahmen bei Leiterplatte und Logik/MPU lässt sich die Herstellungswirkung zusätzlich senken.

Mittelfristig empfiehlt sich eine hybride Sensor-Edge-Architektur für anspruchsvollere Funktionen: Der Sensor extrahiert die wesentlichen Merkmale energieeffizient, während Edge-Beschleuniger komplexe Verarbeitungsschritte übernehmen. So lassen sich MIMO-Winkelmessung und robustes Mehrziel-Tracking schrittweise erschließen, ohne die Grundprinzipien der Energieeffizienz zu unterlaufen. Ergänzend sollten lieferantenseitige Product-Carbon-Footprints (PCF) konsequent eingefordert und PCB-Fertigungsoptionen mit geringerer Umweltlast genutzt werden, um die Herstellung weiter zu optimieren.

Langfristig stellt der Demonstrator einen übertragbaren Baustein für ressourceneffiziente Sensorik dar: Ein- bis Zweikanal-Systeme können häufig direkt auf µC verlagert werden, während hochkanalige, latenzkritische Anwendungen von der Sensor-Edge-Aufteilung profitieren. Für die Verwertung sind anwendungsnahen Demos (z. B. Positionierung, Volumenmessung), die Identifikation von Validierungspartnern und eine klare Angebotslage entscheidend. Der Kurs ist damit gesetzt: Grünere Signalverarbeitung wird zur gestaltbaren Eigenschaft – technisch belastbar, ökologisch wirksam und industriell anschlussfähig.

## 8. Danksagung

Dieses Whitepaper entstand im Rahmen des Verbundprojekts „Green ICT @ FMD – Kompetenzzentrum für ökologisch nachhaltige IKT“. Wir danken dem Bundesministerium für Forschung, Technologie und Raumfahrt (BMFTR) für die Förderung. Das Vorhaben wird unter dem Förderkennzeichen 16ME0494 gefördert und durch die Forschungsfabrik Mikroelektronik Deutschland (FMD) koordiniert. Unser besonderer Dank gilt den Verbundpartnern für die konstruktive Zusammenarbeit sowie dem Fraunhofer IZM für die Unterstützung bei der Ökobilanzierung. Die Verantwortung für den Inhalt dieser Veröffentlichung liegt bei den Autorinnen und Autoren.

## Quellen

- [1] F. J. Harris, On the use of windows for harmonic analysis with FFT, IEEE, 66(1), 1978, pp. 51–83.

- [2] M. Gasior, J. L. Gonzalez, Improving FFT Frequency Measurement by Parabolic Interpolation, CERN, BIW 2004

- [3] J. I. Brown; D. C. Rife, R. R. Boorstyn, Tone Estimation, IEEE Trans. Info Theory, 20(5), 1974.

- [4] W. Grandke, Interpolation Algorithms for FFT Spectra, IEEE Trans. Measurement, 32(2), 1983.

- [5] TI, Interleaved Data Defense; ADC-Skew Resolution (Application Note SLAA105).

- [6] NI Whitepaper zu Timing/Jitter Management.

- [7] Arm, CMSIS-DSP Library (CMSIS-DSP Repo).

- [8] STMicroelectronics, STM32H735 Datasheet: Cortex-M7 (Floating DSP).

- [9] ISO 14040, Environmental Management, Life Cycle Assessment Principles.

- [10] ISO 14044, Life Cycle Guidelines und Reporting Frameworks.

- [11] UBA, Strom-Emissionswerte Deutschland (Bündnis CO<sub>2</sub>-Index 0,4).